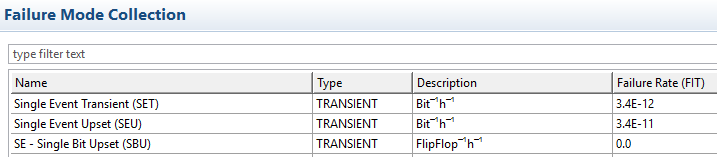

| Transient base failure rates | Transient failure rates can now be derived from the number of sequential

elements (i.e. flip-flops, logical gates) of an IP Design. The individual soft error

rates for SEL, SET, SEU, etc. can be specified by means of base failure rates per

element (gate/FF/bit) and connected to a transient failure in the analysis.

|

| Configurable FMEDA exchange | The handover of FMEDA/SPF and LF metrics data from semiconductors to integrators of a chip ("tier 1") is now supported by a dedicated export DC operation. This new feature can bundle the relevant data into a separate project, so that it can be adapted to the system context (e.g. mission profile, safety mechanisms) while at the same time protecting detailed design IPs. |

| Automated QKit for semiconductor features | The medini "Tool Qualification Kit" is continuously adapted to the new features of the tool. With the license change and specific application cases for semiconductors, we have introduced a separate "Semiconductor Test Suite" that takes specifically care on all the features related to IP Designs. |

| New License model | Version 19.2 introduces two new license types that are tailored to semiconductor workflows. The "Semiconductor Enterprise" license and the "DC Configurator" support specifically the workflow of analyzing a chip design with real IP Design data and adapting the chip level analysis for an integration context. Please contact ANSYS sales for getting more information. |