Duty Cycle Distortion

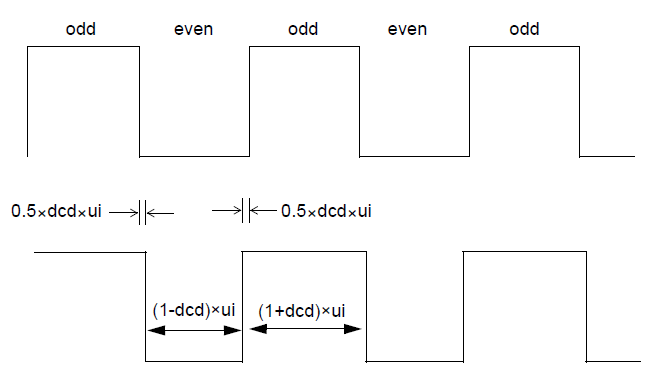

Duty cycle distortion or DCD is a systematic variation in the duty cycle of the transmitter clock, the proportion of time that the clock is high. By default, the duty cycle is 50% (upper waveform in Figure 1). The DCD parameter on the Eye source specifies the duty cycle distortion as a fraction of the unit interval (UI). The transmitted bits can be numbered from 1 to N; bit numbers 1, 3, 5, etc. are odd bit positions, numbers 2, 4, 6, etc, are even bit positions. (Note that the odd and even positions do not in general correspond to particular bit values (0 or 1), except when the signal is a pure clock.)

For both QuickEye and VerifEye, the Circuit solver reads the DCD parameter (DCD as a fraction of the UI) or the DCD_TIME parameter (DCD as an absolute time in seconds.) A DCD_TIME parameter value is converted to DCD as a fraction of the UI. The solver computes the offset value (0.5×DCD×UI). The offset value is then subtracted from all even bit positions and added to all odd bit positions (lower waveform in Figure 1).

Figure 1. Clock Waveforms. The Lower Trace shows Duty Cycle Distortion.