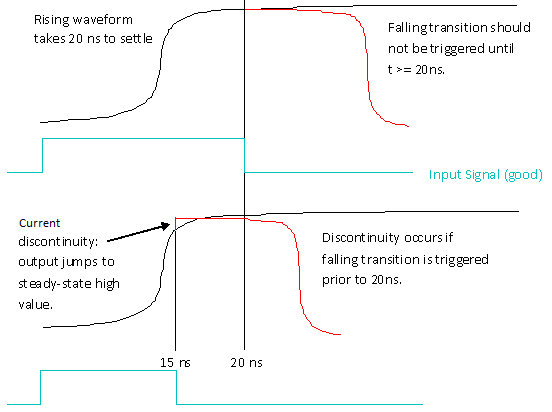

Be careful to ensure the frequency of the input signal does not exceed the capabilities of the IBIS model. The frequency of the input signal must consider the time required for the output to settle. Whenever a transition from high to low or from low to high is triggered by the input signal, the output jumps to the steady-state current value from which the next transition starts. However, the actual waveform requires a settling time period to reach the steady-state high or low voltage. If the input then changes state too soon, the next transition occurs before the initial transition has settled to its steady-state value. This can lead to non-physical voltage slew rates and other unexpected simulation results.

For example, if the IBIS model takes 20ns to complete a rising transition, the input signal should stay in the high state (1V) for at least 20ns after a low-to-high-transition. If instead the input goes back to low after only 15ns, the behavior at the high-to-low transition creates a non-physical slope change in the output signal. Since the initial rising transition has not completed at 15ns, the output has not settled at the steady state from which the falling transition is to occur. The too-early falling transition causes the output current to jump discontinuously to the high value.